A bus is a communication system that transfers data between components in a computer. It consists of both hardware (wires) and software (protocol). Buses are used internally to connect individual components (for example, CPU to memory) and externally to other devices.

A bus typically consists of three signal line types:

- Data bus: exchange data.

- Address bus: select which peripheral or register of a peripheral.

- Control signals: synchronize and identify transactions, as part of the protocol.

Using these signals, a bus operation looks like:

- Manager sends desired address on address bus and sets control signals. Then waits for response.

- Subordinate sends back data on data bus and control signals.

- Manager reads data, starts another communication cycle.

To avoid waiting, one common design is valid-ready:

- The sender sets a VALID signal when it’s sending a message.

- The recipient sets a READY signal when it’s ready to receive.

- Data is only sent when both VALID and READY are set, otherwise both sides can do other work.

AXI

One example protocol is AXI, which is part of the AMBA bus family and used by Arm. Its components include:

- Manager: the component that initiates transactions.

- Subordinate: the component that receives transactions.

- Interconnect: a component that connects managers with subordinates.

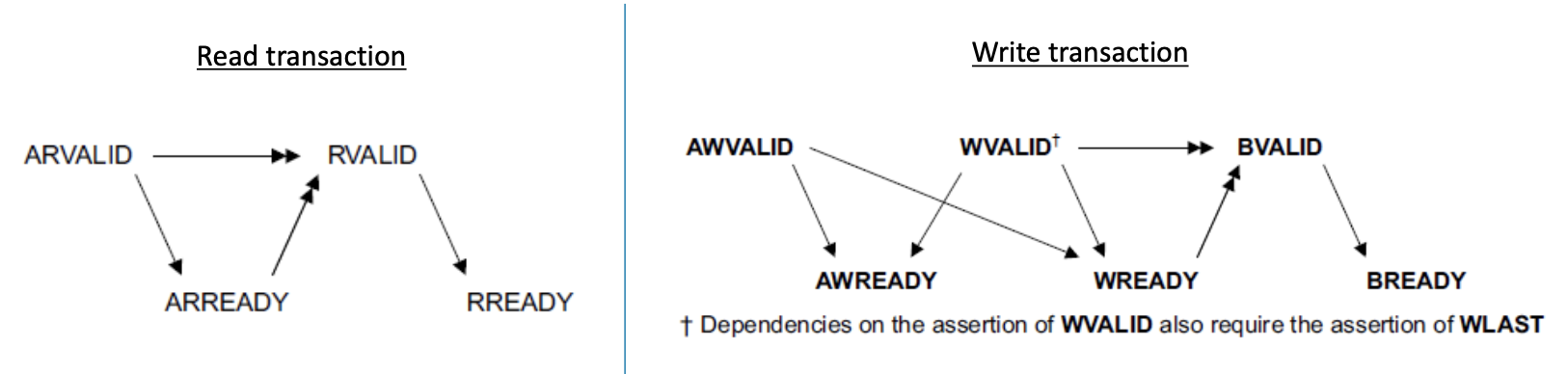

The AXI protocol is burst-based and uses the following independent transaction channels:

- Read address (AR): the address to read.

- Read data (R): the data that was read.

- Write address (AW): the address to write to.

- Write data (W): the data to write.

- Write response (B): the result of writing.

To read, the manager sends AR and the subordinate responds with R. To write, the manager sends AW and W, and the subordinates responds with B. Each of these channels use valid-ready to communicate.

For futher coordination, each AXI component has clock (ACLK) and reset (ARESETn) signals. Input signals are sampled on the rising clock edge, and output signal changes must occur after the rising edge.